# **CS61C Summer 2013 Final Exam Rubric**

| Your Name:          | Peter Per  | fect  |          | SID: _00000000 |         |       |  |  |

|---------------------|------------|-------|----------|----------------|---------|-------|--|--|

| Your TA (Circle):   | Albert     | Kevin | Justin   | Shaun          | Jeffrey | Sagar |  |  |

| Name of person to y | our LEFT:  |       | Sammy    | Student        |         |       |  |  |

| Name of person to y | our RIGHT: |       | Larry Le | arner          |         |       |  |  |

This exam is worth 90 points and will count for 26% of your course grade.

The exam contains 7 questions on 14 numbered pages. Put all answers in the spaces provided. Some pages are intentionally left blank for scratch space.

**Question 0:** You will receive 1 point for properly filling out this page as well your login on every page of the exam.

| Question | Points (Minutes) | Score |

|----------|------------------|-------|

| 0        | 1 (0)            |       |

| 1        | 23 (48)          |       |

| 2        | 9 (20)           |       |

| 3        | 15 (30)          |       |

| 4        | 12 (20)          |       |

| 5        | 17 (36)          |       |

| 6        | 13 (26)          |       |

| Total    | 90 (180)         |       |

All the work is my own. I had no prior knowledge of the exam contents nor will I share the contents with others in CS61C who have not taken it yet.

| Signature: |  |  |  |

|------------|--|--|--|

|------------|--|--|--|

# **Question 1:** Potpourri – Hard to Spell, Nice to Smell (23 points, 48 minutes)

## a) (3 points) MOESI on Through This Problem

Our computer has two cores, each with a 32B direct-mapped cache with 16B blocks using write-back and write-allocate policies. The MOESI protocol is implemented with invalidation of other caches on write, and the caches are empty at the beginning of the program. arr is a block-aligned array of ints.

Fill out the status of the blocks in each cache. Indicate any memory locations that are not up-to-date as well. The first two rows have been done for you, using the abbreviations "C" for cache and "B" for block.

| After Operation      | Core 1 \$ State            | Core 2 \$ State              | Out-of-date Mem Locations |  |

|----------------------|----------------------------|------------------------------|---------------------------|--|

| C1: read from arr[0] | B0: Exclusive              | B?: Invalid                  | nono                      |  |

| CI. redu mom arr[0]  | B?: Invalid                | B?: Invalid                  | none                      |  |

| C2:                  | B0: Exclusive              | B1: Modified                 | arr[5]                    |  |

| C2: write to arr[5]  | B?: Invalid                | B?: Invalid                  | arr[5]                    |  |

| C2: write to arr[2]  | B0: Invalid<br>B?: Invalid | B0: Modified<br>B1: Modified | arr[5], arr[2]            |  |

| C1: read from arr[3] | B0: Shared<br>B?: Invalid  | B0: Owned<br>B1: Modified    | arr[5], arr[2]            |  |

#### Follows directly from MOESI state definitions with cache invalidations.

+0.25 points per element in box, question score rounded up to nearest multiple of 0.5.

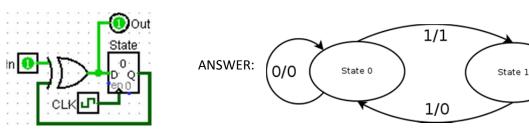

## b) (4 points) Answer the following questions based on the FSM circuit shown below:

i. (2 points) Draw the FSM state diagram (assume the initial state shown) in the space below:

-0.5 points per incorrect transition, -0.5 for incorrect binary state representation, min score of 0.

ii. (2 points) Let  $t_{\rm setup} = t_{\rm hold} = 50$  ps and  $t_{\rm XOR} = 20$  ps. If we run this FSM on a 4-GHz processor and the input arrives  $t_{\rm hold}$  after the clock triggers, what are the maximum and minimum  $t_{\rm clk-to-q}$  for the register to ensure proper functionality?

Min: \_\_\_30ps\_\_\_\_ Max: \_\_180ps\_\_\_

For proper functionality:  $t_{

m hold} \leq t_{

m clk-to-q} + t_{

m XOR} \leq T - t_{

m setup}$  So min =  $t_{

m hold} - t_{

m XOR}$  = 30 ps and max =  $T - t_{

m setup} - t_{

m XOR}$  = 180 ps.

+1 point per blank, all or nothing.

0/1

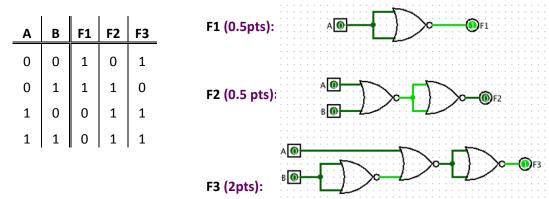

## c) (3pts) Implement the following truth table functions using only NOR gates (fewer is better)

F1 = A', which can be accomplished with A NOR A or A NOR 0.

F2 = A OR B, which can be accomplished with F1(A NOR B) = (A NOR B)'.

F3 = A+B' using product of sums, which can be accomplished with F2(A,F1(B)).

(-0.5 points for using more gates than the solution. This penalty was applied max once for all circuits)

(-1.5 for not using NOR gates or not drawing gates)

(-1 for correctly writing A OR B' or A OR (A NOR B) for F3 but drawing an incorrect diagram)

## d) (5 points) Hamm It Up

i. (2 points) What's the correct data word given the following SEC Hamming code: 0101000?

Parity group 1: xor(0,0,0,0) = 0. Parity group 2: xor(1,0,0,0) = 1. Parity group 4: xor(1,0,0,0) = 1. So error in bit 6 means correct code word is  $01\underline{0}1\underline{0}10$ , with data word 0010.

-0.5 pts for writing down the entire code word. The problem clearly says *data* word.

| 0010 |  |

|------|--|

|      |  |

You are analyzing a new error detection/correction scheme for 4 bits of data  $(d_1d_2d_3d_4)$ , where you store *two* parity bits  $(d_1d_2d_3d_4p_1p_2)$  with  $p_1 = xor(d_1,d_2,d_3,d_4)$  and  $p_2 = xor(d_1,d_2,d_3,d_4,p_1)$ . For example, if the data bits were 1011, the code word would be 101110.

Notice that the  $6^{th}$  bit  $(p_2)$  should *always* be 0 due to parity.

- ii. (1pt) What fraction of all code words is valid?

Each data word maps to exactly 1 valid code word. 2<sup>4</sup> valid code words in 2<sup>6</sup> code words.

- iii. (1pt) What is the minimum Hamming distance between valid code words? \_\_\_\_2\_\_\_\_ Change 1 data bit and p<sub>1</sub> to get to another valid code word.

- iv. (1pt) What is the *maximum* number of errors we can *detect*? \_\_\_\_2 Can detect 1 error in  $d_1d_2d_3d_4p_1$  as well as a simultaneous error in  $p_2$  (should always be 0).

| e) (           | 5 points) There's Loot to be Had Let's RAID It!                                                                                                                                                                                                                  |                      |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| You            | are using RAID with 8 equally-sized disks and block-striping in 32-bit chunks.                                                                                                                                                                                   |                      |

| i.             | (1pt) Which RAID level(s) can you <i>not</i> use? (-0.5 per wrong answer) Need to be able to block stripe.                                                                                                                                                       | 1, 2, 3              |

| ii.            | (1pt) With which viable RAID level(s) can you to store the <i>most</i> data? No redundancy, so can use all of disk space for data.                                                                                                                               | 0                    |

|                | (3,4,5 accepted if 0 was written for part i)                                                                                                                                                                                                                     |                      |

| iii.           | (1pt) With which viable RAID level(s) can you store the <i>least</i> data?  RAID 6 requires TWO parity blocks per stripe.                                                                                                                                        | 6                    |

|                | (1 accepted if it was not included for part i)                                                                                                                                                                                                                   |                      |

| iv.            | (2pts) If using RAID 5, how many disk reads and writes are there for writing 8 the same stripe?                                                                                                                                                                  | bytes of data within |

|                | 8 B of data spans two disks. In order to calculate new parity block, need to reblocks and old parity block. Then write new data blocks (2) and parity block.                                                                                                     | ead both old data    |

|                | 1 pt per blank1 for 2/2 or 4/4                                                                                                                                                                                                                                   |                      |

| We r           | 3 pts) Solve for the maximum controller overhead to meet the following need disk latency under 18 ms while reading 800 B of data. The hard drive spir a seek time of 2.5 ms and transfer rate of 80 KB/s (SI prefix). Don't forget unit                          | ns at 6000 rev/min   |

|                |                                                                                                                                                                                                                                                                  | 0.5ms                |

| rotat<br>trans | roller overhead $\leq$ disk latency – seek time – rotation time – transfer time ion time = 0.5/rpm * (60 sec/1 min) = 0.005 s = 5 ms after time = data size/transfer rate = 0.01 s = 10 ms roller overhead $\leq$ 18 – 2.5 – 5 – 10 ms = 0.5 ms                  |                      |

| (+1 p          | point for correct rotation time calculation of 5ms) point for correct transfer time calculation of 10ms) point for correct formula Latency = Seek + Rotation + Transfer + Overhead) for minor incorrect math. This penalty was applied once for the whole proble | m)                   |

# Question 2: MIPStifying (9 points, 20 minutes)

Answer the questions below about the following MIPS function. Answer each part separately, assuming each time that mystery() has not been called yet.

```

mystery:

andi $a0, $a0, 3

1

$t0, $0, 1

2

ori

$t0, $t0, 6

3

sll

4

Lbl1: beq

$a0, $0, Lb12

5

sll

$t0, $t0, 5

$a0, $a0, -1

6

addi

7

j

Lbl1

8

Lbl2: la

$s0, Lb13

8

$s1, 0($s0)

lw

9

add

$s1, $s1, $t0

$s1, 0($s0)

10

SW

11

Lbl3: add

$v0, $0, $0

12

$ra

jr

```

- b) (1 pt) Write an equivalent *arithmetic* (not logical) C expression to instruction 1.

a0 = \_\_\_a0 % 4\_\_\_\_

- 0.5 pts given for using the modulus operator with wrong arguments. 0 pts for using bitwise and (&) because the question specifically stated not to use logical expressions.

- c) (2 pts) Which instruction field gets modified when mystery is called with \$a0 = 3? \_\_\_rs\_\_\_\_\_ Executing mystery with \$a0 = 3 results in \$t0 being shifted left by 21. The 1 bit in \$t0 was aligned with the last bit of the rs field, so the addition incremented rs by 1, changing \$0 to \$at.

1 pt was given for off-by-one errors (rt), and 0.5 pts were given for opcode and rd.

d) (0.5 pts) How many times can mystery(2) be called before the behavior of mystery() changes?

\_\_\_0 or 1\_\_\_\_

Calling mystery(2) increments rt of line 11, which changes the return value of the function. Based on both the argument that we can't claim that the function changes before it is executed and the point value of the question, either 0 or 1 was accepted for full credit.

| e) | (2 pts) How many times can mystery(0) be called before the behavior of mystery() changes? |  |

|----|-------------------------------------------------------------------------------------------|--|

|    | 31                                                                                        |  |

Calling mystery with \$a0 = 0 adds 1 to the shamt field, which is unused in an add instruction. The behavior of the function won't change until the sum overflows into the rd field, which will take 32 times. Thus, mystery can be called 31 times before the behavior changes.

0.5pts were deducted from an answer of 32.

f) (3 pts) A program calls mystery with the following sequence of arguments: 0, 1, 2, 3, 4, 5. What MIPS instruction gets stored in memory?

\_\_add \$a0, \$at, \$at\_\_\_

The first instruction takes the modulus of \$a0 by 4, so it was equivalent to calling the function with arguments 0, 1, 2, 3, 0, 1. Thus, rs and rt incremented by 1 while rd and shamt are incremented by 2.

1.5 pts were given for finding the correct instruction and 1.5 pts were given for finding each correct argument. Those who wrote the correct instruction but no arguments received a penalty of 0.5 pts. A common mistake was to forget about the modulus—those answers received 2pts. Partial credit was given in certain cases if work was shown.

# **Question 3:** To Be Without Parallel... Means You're Slow (15 points, 30 minutes)

#### a) SIMD and OpenMP

} Property;

Four CEOs are playing the board game Monopoly, where the object of the game is to own properties and gain profits from them. You are in charge of keeping track of the CEOs' finances and wish to parallelize this task. All memory accesses are valid. Assume sizeof(int) = 4.

Every round we must give each CEO the amount of money that he has earned from each of his properties. To do this, we add the property's profit into the CEO's balance and then set the profit to zero for the next round using the following function (+0.5 points per line – part i):

```

void collect_profits() {

for(int i = 0; i < NUMPROPS; i+=2) {

balance[props[i].owner] += props[i].profit;

props[i].profit = 0;

balance[props[i+1].owner] += props[i+1].profit;

props[i+1].profit = 0;

}

}</pre>

```

- i. (1 pt) Perform a 2-fold unrolling of the loop by filling in the blank spaces above. You may edit the looping conditions if you need to (cross out and write in changes). Assume NUMPROPS is a multiple of 2.

- -0.5 pt if NUMPROPS edited improperly-0.5 pt if don't increment i+=2 each iteration+0.5 pt per line, 0 pt minimum

- ii. (2 pts) \_mm\_loadu\_sil28 loads 128-bits of data into a vector. If we wish to use **three** of these instructions to load from props[] every iteration of our loop, how many fold must we unroll the original loop? Answer n if performing an n-fold unrolling. \_\_\_\_6\_\_\_

Since our Property struct is 64 bits wide, we can load two of them at a time with each 128 bit SIMD \_mm\_loadu\_si128 instruction. Therefore we can load 6 properties with 3 \_mm\_loadu\_si128 instructions, which would require a 6-fold unrolling.

iii. (1 pt) You slap a #pragma omp parallel for statement on the original for loop. Circle the effect on execution below and provide a one phrase/sentence explanation. No credit without explanation.

Correct; Correct; Almost always Segfault

**Explanation:** We have a data race for writes to balance.

0.5 pts for claiming "data dependency" on balance.

iv. (1 pt) Now you additionally add a #pragma omp critical statement around all writes to balance[]. What is the new effect on execution? No credit without explanation.

Correct; Correct; Almost always Segfault

**Explanation:** Our threads effectively proceed sequentially, but they do compute the correct result. Slower due to cache invalidations on writes to balance.

0.5 pt for "false sharing", because writes to the same location in balance by different threads wouldn't be considered false sharing.

### b) MapReduce

Suppose that given a large social network dataset, you wish to generate recommendations for yourself by looking at the "Likes" of your friends. You wish to exclude your own likes so that the recommendations are useful. Unfortunately, your input dataset consists of everyone on the social network, not just your friends. Assume that you have access to a global person\_id for yourself, YOUR ID.

Conceptually, you can think of the map as filtering the overall dataset to just you and your friends, while the reduce will filter out common "Likes" between you and your friends.

```

You have access to the following special methods:

```

Feel free to access members of lists and tuples using array syntax.

i. (1 pt) The input to the map function is (key = person\_id, value = (friend\_list, likes)). How many times will a friendship between two people show up in the input data? \_\_\_\_2\_\_\_

Once as (you, friend) and once as (friend, you).

ii. Fill in the MapReduce functions below using Java-like pseudocode:

```

map(key, value){

friend_list = value[0];

likes = value[1];

person_id = key;

for (friend: friend_list) {

if (person id == YOUR ID) {

emit (( YOUR_ID, ___friend____), (0, likes));

} else if (___friend==YOUR_ID_____) {

emit ((__YOUR_ID___, ___person_id___), (1, likes));

} // 1 point per above blank, -1 for swapping YOUR_ID, person_id

}

}

reduce(key, values){

emitValues = ____sortOnValues1(values)____; // 1 point

emit(key, removeAll(_emitValues[1][1]___, __emitValues[0][1]___));

//

2 points

2 points

```

Only emit from map if you are in the friend pair. Include 0 or 1 in value to differentiate whether they are your likes or your friend's likes. Sort on this 0/1 value in reduce to remove your likes from your friend's likes.

- -1 for using something like friend list.contains(YOUR ID) (produces too many emits)

- -1 for indexing errors

- -0.5 for VERY minor indexing errors

- -1 for incorrect ordering in final emit (but otherwise correct)

- -0.5 for using values instead of emitValues

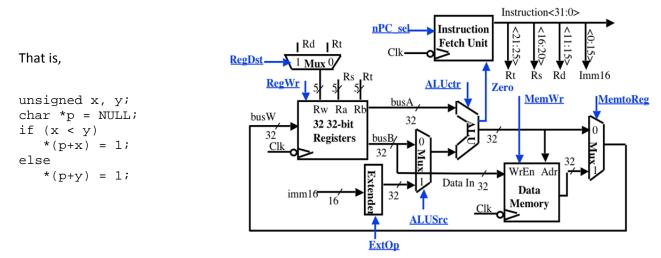

# **Question 4:** Off the Beaten Datapath (12 points, 20 minutes)

Add the instruction stones (store one smaller) to the single cycle datapath, which stores a 1 at the address of the smaller value between two specified registers. **Ignore pipelining.**

NOTE: A surprisingly large amount of students misinterpreted the instruction and updated the minimum register itself (rather than the memory address that the register contained). The sample C code should have made the correct behavior unmistakable; however it was still missed in about 20% of the exams. If the behavior of the instruction was misinterpreted, we deducted a flat 3 points for the mistake and then graded the problem as if we had asked for the misinterpreted behavior.

a) (2 points) Write out the assembly syntax and RTL for this instruction. Don't forget about the PC!

Syntax: stones rs, rt RTL: Mem[(R[rs] < R[rt]) ? R[rs] : R[rt]] = 1; PC = PC+4;

Syntax was worth .5 points, all or nothing. If actual registers were used instead of the general \$rs,\$rt, credit was still granted. If the "\$" symbols were left off, credit was still granted. We were lenient here.

RTL was worth 1.5 points; updating the PC was worth .5 points, and the RTL for the memory update was worth 1 point. If the RTL was syntactically incorrect, but still had the correct logic, full credit was given. Minor errors in logic received .5 point deductions.

b) (5 points) Change as *little as possible* in the datapath above (draw your changes on the figure) to enable stones. List all your changes below (be concise!). Your modification may use MUXes (define what select bits refer to what inputs), wires, constants, and up to one new control signal, but <u>nothing else</u>. You may not need all of the provided boxes. You cannot modify the ALU (there is no min operation). (2 point per cascaded MUX, 1 point for other MUX).

There were 3 MUXes that needed to be added to ensure this instruction worked correctly and other instructions would still behave properly. Points were awarded if the complete behavior of each MUX (where the inputs came from, where the output went, where the select bit came from and to which input it mapped) could be determined from the description, the diagram, or both. The lack of each of these details resulted in a half point penalty. The MUXes described in (i) and (ii) below were worth 2 points each, while the MUX in (iii) was worth 1 point. The use of additional unnecessary hardware received a .5 point penalty. The use of disallowed hardware (such as comparators or changing the ALU) received only 1 point, as this removed the need for two of the MUXes. Describing the addition of a new control signal was not graded until part (c).

- (i) MUX to select between busA (S=1) and busB (S=0) for input addr to Data Mem. The select bit is the LSB of the ALU output after the sltu instruction (we want the minimum value).

(ii) MUX to select between output of MUX from above (S=1) and ALUOut (S=0) for AddrIn to DataMem. Select bit is new STONES control signal.

(iii) MUX to select between constant 0x1 (S=1) and busB (S=0) for Data In into DataMem. Select bit is new STONES control signal.

(iv) NOT NEEDED

- c) (5 points) We now want to set all the control lines appropriately. List what each signal should be, using 0, 1, X, or an intuitive name. Include any new control signals you added. (0.5 points / signal)

Every signal was worth .5 points, with the exception of ALUctr which was worth 1 point. 1 point was granted for using the instructions sltu, sub, or subu, and .5 was given for the instructions slt, or the words "less than" or "greater than". Signals must have been unambiguous; 0 or 1 for nPC\_Sel was marked incorrect. Signals that did not have an effect on the instruction must have been marked X for credit. Using an extraneous control signal nullified the points for the STONES control signal. STONES was the name of the control signal we came up with; other names were still given full credit.

| RegDst | RegWr | nPC_sel | ExtOp | ALUSrc | ALUctr | MemWr | MemtoReg | STONES |

|--------|-------|---------|-------|--------|--------|-------|----------|--------|

| X      | 0     | PC+4    | X     | 0      | sltu   | 1     | Х        | 1      |

# **Question 5:** Tread Carefully, Thread Carefully (17 points, 36 minutes)

Examine the function prototype and MIPS implementation below.

```

// sets *value = (*value) * 2^pow using shifting instructions

int multMemPow2(int *value, unsigned int pow);

multMemPow2:

$v0, 0($a0)

1

# load value

lw

2

loop: beq $a1, $0, exit # exit condition

sll $v0, $v0, 1

# multiply by 2

3

4

addi $a1, $a1, -1

# decrement counter

$v0, 0($a0)

5

# store result

```

We are using a 5-stage MIPS pipelined datapath with separate I\$ and D\$ that can read and write to registers in a single cycle. Assume no other optimizations (no forwarding, no branch prediction, etc.). The default behavior is to stall when necessary. Branch checking is done during the Execute stage.

For parts (a)-(c), let pow=1. When we ask for clock cycles to execute multMemPow2, we mean from the instruction fetch of lw up to and including the write back of jr.

a) (1 point) How many instructions are executed in multMemPow2?

```

pow=1, so execute lw, beq, sll, addi, sw, j, beq, jr \rightarrow 8 instr ____8____

+0.5 pt if answered 13 for pow=2.

```

b) (4 points) How many clock cycles does it take to execute multMemPow2?

(See pipelining table below) 18

Potential Structural Hazards: none, MIPS is great!

6

7

j

exit: ir

loop

\$ra

Potential Data Hazards: 1-3 (taken care of by stalls for branch control hazard),

3-5 (needs 1 stall because already one instr in-between)

Potential Control Hazards: beq (2 stalls because only know next instr after EX stage),

j (1 stall because get target addr in ID stage)

So for the 8 instructions listed above, you get 8 instr + 4 fill/drain + 6 stalls = 18 cycles.

| Cycle # | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |

|---------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|

| lw      | F | D | Χ | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |

| beq     |   | F | D | Χ | M | W |   |   |   |    |    |    |    |    |    |    |    |    |

| sll     |   |   |   |   | F | D | Χ | M | W |    |    |    |    |    |    |    |    |    |

| addi    |   |   |   |   |   | F | D | Χ | М | W  |    |    |    |    |    |    |    |    |

| sw      |   |   |   |   |   |   |   | F | D | Χ  | M  | W  |    |    |    |    |    |    |

| j       |   |   |   |   |   |   |   |   | F | D  | Χ  | M  | W  |    |    |    |    |    |

| beq     |   |   |   |   |   |   |   |   |   |    | F  | D  | Χ  | M  | W  |    |    |    |

| jr      |   |   |   |   |   |   |   |   |   |    |    |    |    | F  | D  | Χ  | M  | W  |

| +1  <br>+1  <br>+0. | pt fo<br>pt fo<br>5 pt  | or recogn<br>or recogn<br>for the | nizing the 3-5 da<br>nizing the j stall.<br>nizing the two be<br>4 cycle pipeline f<br>ver to part (b) > | -0.5 pt if we<br>eq double s<br>fill/drain. | vrong<br>stalls.            | # of stalls.<br>-0.5 pt if wrong                          |                                       |                                     |                                                               |

|---------------------|-------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------|-----------------------------------------------------------|---------------------------------------|-------------------------------------|---------------------------------------------------------------|

| c)                  |                         | •                                 | onsider the follon                                                                                       | • .                                         | nizatio                     | ons <i>separately</i> .                                   | How ma                                | ny FEWER cy                         | cles are taken for                                            |

|                     | i.                      | Only el                           | ints) Forwarding<br>iminates 3-5 dat<br>in part (b).                                                     |                                             | all. Fu                     | ıll credit given i                                        | f answer                              | matched # c                         | 1of data hazard stalls                                        |

|                     | ii.                     | Only el                           |                                                                                                          | stalls. Flus<br>r the 1 <sup>st</sup> bed   | shing o                     | on an incorrect<br>credit given if                        | answer n                              | natched # of                        | 2<br>Ifter the EX stage, so<br>stalls for 2 <sup>nd</sup> beq |

| d)                  | nev                     | v jump o                          |                                                                                                          | nstruction 6                                | 6 <b>(</b> j 1              | oop). For the f                                           | ollowing                              | candidate in                        | instruction into the astructions, answer <b>C</b>             |

|                     |                         | Instr 3:                          | C_(0.5 pt)                                                                                               | In                                          | str 4:                      | S_(1 pt)                                                  |                                       | Instr 5:                            | _ <mark>G</mark> _(0.5 pt)                                    |

|                     |                         | Storin                            | g different \$v0 ii                                                                                      | n sw Da                                     |                             | zard on \$a1 wit<br>pt if answered                        |                                       |                                     | Works!                                                        |

|                     |                         |                                   | ng questions, ass<br>ne same shared-                                                                     |                                             |                             | _                                                         |                                       |                                     | ously on TWO                                                  |

| For<br>sto          | pow<br>res 2            | n=2, eac<br>2 and 4 i             | ist ALL possible which thread perform the as it eas at the end. Even                                     | ns one load<br>executes. T                  | d and the oth               | two stores. On<br>ner thread can i                        | e thread<br>read *va                  | lue=1, 2, <b>or</b>                 | 4, 8, 16<br>read *value=1 and<br>r 4 and will thus            |

| +1                  | pt fo                   | r each c                          | orrect number,                                                                                           | -0.5 pt for                                 | each a                      | <i>idditional</i> numl                                    | oer.                                  |                                     |                                                               |

|                     |                         |                                   | d thinks he can f<br>npares against th                                                                   |                                             |                             |                                                           | lacing th                             | e 1w with 11                        | and sw with sc.                                               |

| call<br>Aga         | the i<br>11 a<br>ain, c | nteresti<br>again! T<br>one thre  | his saves us from                                                                                        | regardless on the head ead *value           | of wha<br>lache d<br>e=1 ar | nt pow>0 is, so<br>of tracking \$v0,<br>and stores only 2 | will only<br>, since its<br>! in *val | work <i>once,</i> k<br>value also g | ecause you don't ets clobbered by sc. utes. So the other      |

| Ma                  | x scc                   | ore if yo                         | u did not recogn                                                                                         | nize that the                               | ere sh                      | ould be fewer բ                                           | ossible v                             | alues in (f) a                      | nd (e) was 2 pt.                                              |

| Res                 | pon                     | ses:                              | 0 (1 pt)<br>4 (2 pt)                                                                                     | 0,1 (2 pt)<br>4, 8, 16 (1                   |                             | 0,2 (3 pt)<br>4, # other than                             | 2 (2pt)<br>2 (3 pt)                   |                                     |                                                               |

The number in the blank was ignored unless you did not show work or had an egregious math error.

# **Question 6:** It's Virtual Insanity! (13 points, 26 minutes)

Our 32-bit uniprocessor machine has 1 GiB of RAM with 1 KiB pages, a fully-associative TLB that holds 8 entries and uses LRU, and a direct-mapped, write-back *data* cache with 32 B blocks and 32 slots. The *instruction* cache is 256 B and fully-associative with 32 B blocks.

a) (1 point) What is the maximum number of valid entries in the page table for a single process? Answer in IEC.

1 Mi-entries

Page table valid entries set by size of PM. 1 GiB / 1 KiB = 1 Mi-entries.

+0.5 points for 1MiB, +0.5 points for  $2^{20}$

b) (1 point) What is the TLB Reach of our system?

\_\_\_8 KiB\_\_\_\_

8 TLB entries that refer to a 1 KiB page each. TLB Reach = 8\*1KiB.

No partial credit – full credit given for 2<sup>13</sup> B.

Examine the following function. Assume the entire program's code takes the entirety of one page and sizeof(int)=sizeof(int \*)=4.

```

void addConst(int *ptr, char c) {

for(int i = 0; 1; i+=4)

ptr[i] += c;

}

```

\*If all of (c,d,f) were answered as if for i++, -2 points total after the scores for those are added (min 0)

c) (2 points) If ptr[] lives in disk and ptr[0] is page-aligned, what is the TLB hit rate for data accesses only?

\_\_\_127/128\_\_\_

Lives in disk means TLB miss on ptr[0]. Loop jumps 4 ints = 16 B per iteration. 1 KiB/16 B = 64 array indices accessed per page. Since += is a read and a write, 1 TLB miss per 128 memory accesses in a page.

- + 1 pt total for answering 63/64 based on missing that += does read and write

- + 2 pt total for answering 511/512 if answering based on i++ interpretation\*

- d) (2 points) If ptr[] lives in disk and ptr[0] is page-aligned, what fraction of D\$ misses are also TLB misses?

| 1   | <b>/つ</b> | ~ |  |  |

|-----|-----------|---|--|--|

| 1 / | ' -<      | • |  |  |

| _,  | J         | _ |  |  |

|     |           |   |  |  |

From part (c), 1 TLB miss every 128 memory accesses. Lives in disk means not in cache. 32 B/16 B = 2 array indices accessed per cache block. Since += is a read and a write, you have 1 D\$ miss per 4 memory accesses in a cache block. The fraction is then 4/128 = 1/32.

Partial credit only for slight arithmetic errors with work shown, which were evaluated individually.

| fault?                                                                                                                                                                                                        | cause a <b>page</b> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| _                                                                                                                                                                                                             | 4                   |

| ptr[0] is in valid entry in page table, but no mention of where in page. If we assume it is last 3 integer spaces in the page, then the next loop iteration ( $ptr[4]$ ) can cause a page is page is invalid. |                     |

| + 0.5 pt for 256 based on assuming page alignment<br>+ 1 pt for answering 1 based on i++ interpretation*                                                                                                      |                     |

| f) (1 point) If ptr[0] is in physical memory, what is the <i>minimum</i> value of i that could oprotection fault?                                                                                             | cause a             |

| -                                                                                                                                                                                                             | 0                   |

| Even with ptr[0] in valid entry in page table, no mention of access rights. The loop both writes, so will cause a protection fault if the process is missing one of those access rights for                   |                     |

| + 0.5 pt for 4 + 0.5 pt for answering 1 based on i++ interpretation*                                                                                                                                          |                     |

For maximum, assume I\$ already holds all instructions of the loop and that the D\$ is filled with the first entries of ptr[]. The D\$ holds 32 \* 32B = 1 KiB of data = 256 ints.

g) (2 points) If ptr[0] is in physical memory, what is the maximum value of i that causes the first

- + 0.5 pt for answering 32 based on a proposed scenario of one block in the cache

- + 0.5 pt for answering 64, the max number of iterations

cache miss in the loop?

h) (3 points) If ptr[0] is in physical memory, what is the *maximum* value of i that causes the first **TLB** miss in the loop? You may leave your answer as a product.

7\*2^8 \_\_\_\_

256

For maximum, assume TLB is full of page entries needed for our function. Each page holds 1 KiB =  $2^8$  ints. Need one page for code/instructions, so 7 remain for ptr[] entries. So first TLB miss (and replacement) will occur when  $i = 7*2^8$ .

- + 2 pt for answering 2048 based on ignoring the code page

- + 1 pt for answering 256 based on assuming only the page holding ptr[0] was in physical memory

- + 1.5 pt for answering 512 based on counting the number of iterations