## University of California at Berkeley College of Engineering Dept. of Electrical Engineering and Computer Sciences

# EE 105 Midterm I

Fall 2005

Prof. Borivoje Nikolić

October 13, 2005

| Your Name:         |  |

|--------------------|--|

| Student ID Number: |  |

#### Guidelines

Closed book and notes; there are some useful formulas in the end of the exam. You may use a calculator.

You can unstaple the pages with formulas, but do not unstaple the exam.

Show all your work and reasoning on the exam in order to receive full or partial credit.

Time: 80 minutes = 1 hour, 20 minutes.

#### Score

| Problem | Points<br>Possible | Score |

|---------|--------------------|-------|

| 1       | 1420               |       |

| 2       | 20                 |       |

| 3       | 16                 |       |

| Total   | 56                 |       |

# 1. Integrated charge-storage element [14 points]

The following figure shows the cross-section of a PMOS capacitor structure. P+ polysilicon gate covers two regions: region A with gate oxide thickness of 300nm and region B with gate oxide thickness of 3nm respectively. The effective areas of the capacitor over the thick and thin oxide are  $10,000\mu\text{m}^2$  and  $100\mu\text{m}^2$  respectively. Please use the following parameters:  $\phi_{p+} = -550\text{mV}$ ,  $\varepsilon_{\text{Si}} = 11.7$ ,  $\varepsilon_{\text{SiO2}} = 3.9$ ,  $\varepsilon_0 = 8.854 \times 10^{-14} \text{F cm}^{-1}$ ,  $n_i = 10^{10} \text{cm}^{-3}$ .

| 400nm P+                                           | 100 D.                    |

|----------------------------------------------------|---------------------------|

| 300nm SiO <sub>2</sub>                             | 400nm P+                  |

| Region A                                           | Region B                  |

| N <sub>SUB</sub> =10 <sup>15</sup> cm <sup>2</sup> | $N_{SUB} = 10^{18}  cm^2$ |

|                                                    |                           |

|                                                    |                           |

(a) [4 points] What are the flat-band voltages (V<sub>FB</sub>'s) of regions A and B?

$$V_{FBB} = -(\phi_{pq} - \phi_n) = -(-550 - 25 \ln \left(\frac{10^{18}}{10^{10}}\right))_{mV} = 838 mV$$

$$V_{FBB} = -(-550 - 25 \ln \left(\frac{10^{18}}{10^{10}}\right))_{mV} = 1010 mV$$

$$W_{FBB} = 1.01 \checkmark$$

(b) [4 points] What are the threshold voltages (V<sub>T</sub>'s) of regions A and B?

$$V_{TA} = V_{FB} - 2\phi_n - \frac{1}{Cox} J_2 f \mathcal{E}_s N_o (2\phi_n)$$

$$C_{ox} = \frac{\mathcal{E}_{ox}}{f_{ox}}, \quad \mathcal{E}_{ox} = \mathcal{E}_{sio} \mathcal{E}_{o}, \quad \mathcal{E}_s = \mathcal{E}_{si} \mathcal{E}_{o}$$

$$V_{TA} = -0.938 V$$

$$V_{TB} = -0.391 V$$

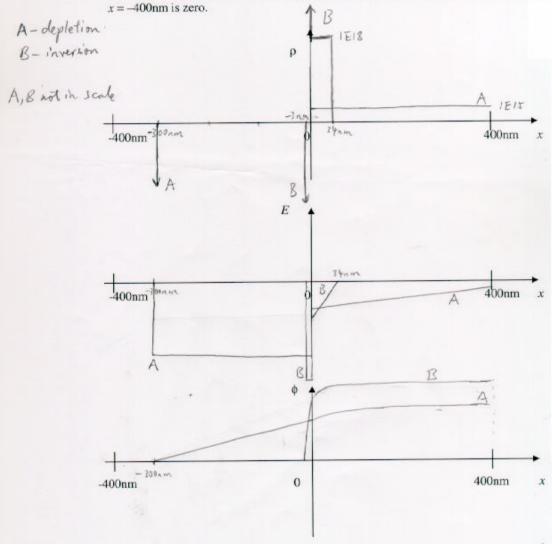

(c) [6 points] Sketch the charge, E-field and potential distribution from x = -400nm to x = 400nm when  $V_G = -0.5$ V for regions A and B. Assume that the potential at x = -400nm is zero.

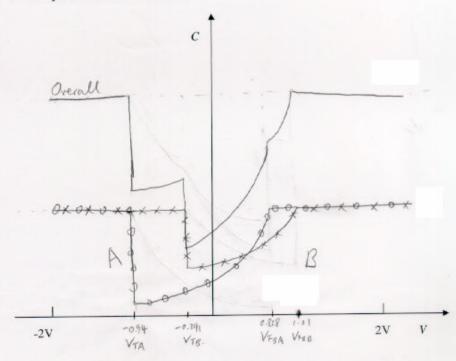

(d) [6 points] Sketch the CV of the whole capacitor structure. Please label the relevant points on the  $\it C$ - and  $\it V$ -axii.

## 2. Semiconductors, pn Junctions and MOS devices [20 pts]

A few useful constants: The permittivity of silicon is  $\varepsilon_s = 1.035 \times 10^{-12}$  F/cm and the permittivity of SiO<sub>2</sub> is  $\varepsilon_{ox} = 3.45 \times 10^{-13}$  F/cm. You can assume mobilities of  $\mu_n = 1500$  cm<sup>2</sup>/(Vs) and  $\mu_p = 500$  cm<sup>2</sup>/(Vs). The saturation electric field for electrons is  $E_{sat} = 1.25 \times 10^4$  V/cm and their saturation velocity is  $v_{sat} = 10^7$  cm/s. Unit charge:  $q = 1.6 \times 10^{-19}$  C,  $n_i = 10^{10}$  cm<sup>-3</sup>.

(a) [4 points] In a silicon resistor made from N-doped silicon doped to  $10^{18}$  per cubic cm, with a length of  $10\mu m$ , a width of  $1\mu m$ , and a thickness of  $0.1\mu m$ , what is the maximum current which can flow?

$$I = A J = A g n V_{sat}$$

$$= (0.1 \times 1) \times 10^{-8} \times 1.6 \times 10^{-19} \times 10^{18} \times 10^{7}$$

$$= 0.0016 A = 1.6 m A$$

(b) [4 points] For a silicon PN junction at room temperature which has one side P doped to a concentration of  $10^{18}$  per cm<sup>3</sup> and the other side N doped to a concentration of  $10^{16}$  per cm<sup>3</sup>, find the depletion depth into both the P side and into the N side.

$$Xdo = Xdnt Xdp$$

$$Xdo = Xdn + Xdn$$

$$Xdo = Xdn + \frac{No}{NA}Xdn = Xdn(1 + \frac{No}{NA})$$

$$Xno = 321.8nm$$

$$Xno = 321.8nm$$

(c) [4 points] What is the <u>qualitative</u> relationship between the width of the depletion region and the conductivity for the N side of the junction in part (b). Briefly explain.

(d) [4 points] Consider two MOSFETs with identical dimensions, but with differently doped substrates; MOSFET A has the substrate doped with  $N_A = 10^{15}$  cm<sup>-3</sup>, and MOSFET B has doping of  $N_A = 10^{16}$  cm<sup>-3</sup>. Assume equivalent bias for both transistors, where both transistors are in saturation. In which case will the same change in  $V_{DS}$  voltage ( $\Delta V_{DS}$ ) cause a larger <u>relative</u> change in the capacitance between the drain and the substrate  $\Delta C_B/C_B$ . Explain your answer.

In your answer.

$$C_{j} = \frac{C_{j} \circ}{\sqrt{1 - \frac{V_{o}}{\phi_{b,i}}}} \stackrel{?}{=} \frac{dC_{j}}{\sqrt{1 - \frac{V_{o}}{\phi_{b,i}}}} = C_{j} \circ \left(-\frac{1}{2}\right) \left(1 - \frac{V_{o}}{\phi_{b,i}}\right)^{\frac{2}{3}}$$

$$\Rightarrow \frac{dC_{j}}{C_{j} \circ} = \frac{1}{2} \frac{1}{\phi_{b,i}} \left(1 - \frac{V_{o}}{\phi_{b,i}}\right)^{\frac{2}{3}} dV_{o}$$

$$\stackrel{?}{\sim} N_{A} \uparrow \Rightarrow \phi_{b,i} \uparrow \Rightarrow A \downarrow \quad B \downarrow$$

$$\stackrel{?}{\sim} N_{A} \uparrow \quad \frac{dC_{j}}{C_{j} \circ} \downarrow$$

(MOSFET A) / MOSFET B (circle one)

(e) [4 points] Which one of the two MOSFETs from (d) would have a larger relative change in effective channel length,  $\Delta L/L$ , under the same change in  $V_{DS}$  voltage ( $\Delta V_{DS}$ ). Explain your answer.

(MOSFET A) MOSFET B (circle one)

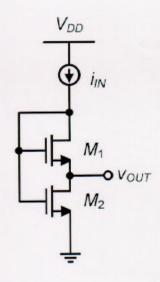

### 3. MOSFET circuit [16 points]

Given:

$$L_1 = L_2 = 0.5 \mu m$$

$W_1 = W_2 = 5 \mu m$

$\mu_n C_{ox} = 100 \mu A/V^2$

$V_{Tn} = 0.5 V$

$\lambda_n = 0 V^{-1}$

$\gamma = 0$

(a) [4 points] In which modes of operation are operating M1 and M2 for  $i_{lN} > 0$ ? Explain your answer.

(b) [8 points.] Find the relationship  $v_{OUT} = v_{OUT}(i_{IN})$ . You do not need to substitute the numerical values.

[4 points] If the current source i<sub>EV</sub> is implemented as simple DC-biased PMOS (c) transistor (W/L = 10,  $\mu_p C_{ox} = 100 \mu A/V^2$ ,  $V_{Tp} = -0.5 \text{ V}$ ,  $\lambda_p = 0 \text{ V}^{-1} \gamma = 0$ ), find the maximum and minimum values of vour, under which the circuit operates correctly, with the supply voltage of  $V_{DD} = 5$ V.

nsistor (W/L = 10,

$$\mu_{PCm} = 100 \ \mu AV^2, V_{Tp} = -0.5 \ V, \lambda_{p} = 0 \ V^1 \ y = 0)$$

, find the ximum and minimum values of  $v_{OUT}$ , under which the circuit operates correctly, with supply voltage of  $V_{OD} = 5V$ .

From b

NP

Very 2 in  $\rightarrow 0$ , Vowt  $\rightarrow 0$  (M1, M2 basely ON)

Vord, man = 0  $\vee$  //

MP is stell in saturation as long as  $V_{B} > -|V_{Tp}| + V_{OI}$

When  $V_{OI}$  is  $v_{OI} = v_{OI} + v_{OI}$

MP:  $v_{IM} = \frac{k}{2} \left( v_{OD} - v_{I} + v_{I} \right) = \frac{k}{2} \left( v_{OD} - v_{IM} \right)$

Vowt =  $\left( v_{I} - v_{I} \right) \left( v_{I} - v_{I} \right) = \frac{k}{2} \left( v_{OD} - v_{IM} \right)$

On the other hand, Vowt =  $v_{I} - v_{I} + v_{I$