· Closed book, closed notes

Score

- · One pocket calculator permitted (no PDAs, laptops, cell phones, or other electronic devices)

- · Show derivations to get partial credit in case of numerical errors

%

- Cross out incorrect attempts (no partial credit for ambiguous derivations)

- · Write results into boxes

- · Take off hats or caps and leave backpacks and electronic devices in isle

- · You may assume that all operational amplifiers are ideal

- Use only positive values (≥ 0) for all passive components (resistors, capacitors, inductors)

- Verify that an assistant receives your completed exam!

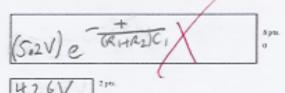

In the circuit below, v<sub>o</sub>(t = 0) = 5.2 V. Derive an expression for v<sub>o</sub>(t), t > 0. Use R<sub>1</sub> = 25 kΩ, R<sub>2</sub> = 75 kΩ. and  $C_1 = 8.8 \mu F$ .

$v_o(t)$  (algebraic result)

$v_o(t = 175 \,\text{ms})$

$$T_{c} = \frac{s_{.2}}{R_{2}} e^{-\frac{t}{R_{H}R_{2}}c_{1}}$$

$$V_{o} = \frac{R_{2} \cdot s_{.2}}{R_{2}} e^{-\frac{t}{R_{H}R_{2}}c_{1}}$$

$$= \frac{s_{.2}}{R_{2}} e^{-\frac{t}{R_{H}R_{2}}c_{1}}$$

2. Capacitor C<sub>1</sub> = 688 mF is used to power a model airplane modeled by resistor R<sub>L</sub> = 387 Ω. Initially the capacitor is charged to v<sub>c</sub> = 7 V. Calculate the fraction r of the initial energy remaining on the capacitor and the voltage v<sub>c</sub> across the capacitor after i<sub>L</sub> has decreased to 75 percent of its initial value. After what time T is this condition reached?

3. You have been hired by SnapOMatic, a fledgling startup making ultra-low power cameras. Your job is to redesign their image compression chip to use less energy.

The current solution consists of  $N=8\times 10^6$  gates. Each gate drives an average capacitance  $C_{in}=2.4$  fF. The image compression algorithm takes  $M = 3 \times 10^{\circ}$  clock cycles (operations) per image. The activity factor, i.e. percentage of gate outputs changing in each clock cycle is  $\eta=24$  %. The maximum operating frequency

$$f_{\rm S,max} = 400 \, \frac{\rm MHz}{\rm V^2} \, \times \, V_{dd}^2. \label{eq:fsmax}$$

a) Calculate the time T<sub>1</sub> and energy E<sub>1</sub> required to compress one image if the processor is operating at its

$$T_1 = 7.5 \text{ MS}$$

$$E_1 = 6.91 \text{ MD}$$

b) The marketing department found a great opportunity for a chip that consumes only  $E_x = 690.8 \,\mu\text{J}$  per compressed image. Calculate the operating frequency  $f_x$  and supply voltage  $V_{dd,x}$  for the existing chip

c) Your friend who took CS61p learned about a parallelized image compression algorithm that has no overhead. What is the number of processors P needed to achieve image compression in 351  $\mu$ s and only 6.9 mJ energy per compressed image? At what frequency  $f_{s,p}$  are they operating?

$$E = 6.9 \text{ MJ} = \frac{1}{2} \text{ CV}^2 \cdot \eta_1 \cdot M_1 \cdot N_1 P$$

$$V^2 = \frac{6.9 \times 10^{-3}}{(.5)(2.4 \times 10^{-3})(.24)(3 \times 10^{-6})(.24)(3 \times 10^{-6})} = 1$$

$$V = 1V$$

$$V =$$

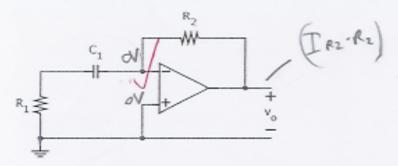

In the circuit below, switch S<sub>1</sub> closes when v<sub>c</sub> increases above 0.7 × V<sub>s</sub>. It then remains closed until v<sub>c</sub> has dropped to  $0.3 \times V_s$ , at which point it opens and stays open until  $v_c > 0.7 \times V_s$ . Find the value of  $C_1$  such that the switch opens every  $6.2 \mu s$  in steady state.

Use  $R_1 = 7.9 \text{ k}\Omega$ ,  $R_2 = 2.8 \text{ k}\Omega$  and  $V_s = 3.2 \text{ V}$ .

$$C_1 \ln \left(\frac{7}{3}\right) \left(R_1 + R_2\right) = 6.2 \times 10^{-6} S^{-1} + 11 + 12$$

$$C_1 = .68 \text{ nF}$$

= 6.84×10<sup>-10</sup> F

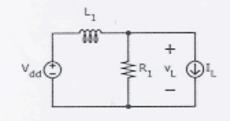

5. In this problem we design a "step down converter" (Buck converter) to efficiently convert the input voltage V<sub>s</sub> = 60 V to a lower value v<sub>o</sub> = 20 V) Such circuits are employed in the familiar "power bricks" used to power laptops and gadgets from the grid. In the diagram below the switch is controlled by a periodic waveform. It is closed for a period T<sub>1</sub>, followed by a period T<sub>2</sub> = T − T<sub>1</sub> during which it is open, with T = T<sub>1</sub> + T<sub>2</sub> 2.4 µs. The diode D<sub>1</sub> acts like a "valve": current passes for v<sub>d</sub> ≥ 0 V; for v<sub>d</sub> < 0 V the diode behaves like an open circuit.</p>

Assume that the circuit operates in "steady state", i.e. the voltage and current waveforms in the circuit repeat with period T. To simplify the analysis, assume that the output voltage  $v_o$  is constant and equal to the design value specified above. This leads to minimal errors when the ripple is small. In practice we would verify the circuit with SPICE to check if all assumptions are valid and we have not made design errors.

a) Find T<sub>1</sub> and T<sub>2</sub>.

$$T_1 = \begin{cases} 8 \text{ MS} & \text{Spea} \\ 12 & \text{Spea} \end{cases}$$

$T_2 = \begin{cases} 12 & \text{Spea} \\ 12 & \text{Spea} \end{cases}$

b) Find the minimum value of L<sub>1</sub> that results in Δi<sub>L</sub> = 34 mA.

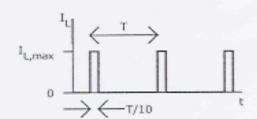

The supply current flowing into digital circuits consists of large spikes with magnitude I<sub>L,max</sub> at the beginning of each clock cycle of duration  $T = 1/f_s$ . The circuit below shows a simplified model of this behavior, consisting of current source  $I_L$  that models the current spikes, and resistor  $R_1$  that models the constant part of the supply current flowing into the circuit. Also included in the model are the power supply  $V_{dd}$  and the wiring inductance  $L_1$ .

Parameter:  $V_{dd} = 1.2 \text{ V}$ ,  $L_1 = 3.8 \text{ nH}$ ,  $R_1 = 9.8 \Omega$ ,  $I_{L,max} = 3.9 \text{ A}$ ,  $f_s = 3 \text{ GHz}$ .

a) Calculate the minimum value of v<sub>L</sub> in steady state.

b) (15 points) For the digital circuit to operate properly, it is necessary that  $v_{L,min} > 0.9 V_{dd}$  at all times. Propose a circuit modification that accomplishes this goal. You are only allowed to add circuit components (only capacitors and inductors are available). Use the minimum number of components required to meet the specification and use the minimum required value for all components. Specify all component values. Suggestion: to simplify the analysis, you may assume that  $v_L = V_{dd}$  at the start of each clock cycle. In practical situations, the error from this approximation is usually negligible. Of course you would verify this using e.g. a circuit simulator.

honge voltageby . I of its inva vale