| Your Name:                                                                   |      |                                            | (1)   | /20 |

|------------------------------------------------------------------------------|------|--------------------------------------------|-------|-----|

|                                                                              |      |                                            | (2)   | /20 |

| NIVERSITY OF CALIFORNIA AT BERKELEY                                          |      |                                            | (3)   | /20 |

| RELEY • DAVIS • IRVINE • LOS ANGELES • RIVERSIDE • SAN DIEGO • SAN FRANCISCO |      | SANTA BARBARA • SANTA CRUZ                 | (4)   | /20 |

| Department of Electrical Engineering and Computer Sciences                   | 1999 | CS 150 - Spring 1996<br>Prof. A. R. Newton | TOTAL | /80 |

## Ouiz 2

Room 10 Evans Hall, 2:10pm Tuesday April 2 (Open Katz only, Calculators OK, 1hr 20mins)

Include all final answers in locations indicated. Use space provided for all working and state all assumptions. If necessary attach additional sheets by staple at the end. BE SURE TO WRITE YOUR NAME ON EVERY SHEET.

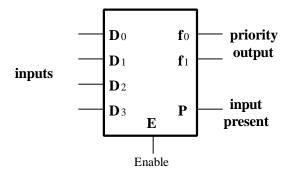

(1) You are to design a **four-input priority encoder**, shown below, such that when two inputs,  $D_i$  and  $D_j$ , are high simultaneously,  $D_i$  has priority over  $D_j$  when i>j. The encoder produces a binary output code ( $f_1$   $f_0$ ) corresponding to the input that has the highest priority. The circuit should also have an enable input, E, such that ( $f_1$   $f_0$ ) are set to (00) when E is low, and an output P which indicates the presence of data (1's) on any of the inputs.

(a) Show a **truth-table** for the priority encoder, in terms of  $D_0$  to  $D_3$  only, and derive the **logic equations** for  $f_0$  and  $f_1$ . Express the logic equations using a **minimum number of literals**.

| 1(a) (10pts)      |                                           |

|-------------------|-------------------------------------------|

|                   |                                           |

|                   |                                           |

|                   |                                           |

|                   |                                           |

|                   |                                           |

| $\mathbf{f_0} = $ | $\mathbf{f_1} = \underline{\hspace{1cm}}$ |

| schematic, using a minimur complements are not avail | number of NAND, OR, and inv<br>ble. | verter gates only. Assume |

|------------------------------------------------------|-------------------------------------|---------------------------|

| 1(b) (10pts)                                         |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

|                                                      |                                     |                           |

(b) Draw a schematic diagram for the entire priority encoder, including output P and input E in the

| Your Name:                                                                     |             |         |         | _        |                                  |

|--------------------------------------------------------------------------------|-------------|---------|---------|----------|----------------------------------|

| (2) (a) For the following state table,                                         | where x is  | the inp | out and | Z is th  | ne output:                       |

|                                                                                | PS          | N       |         | Z        |                                  |

|                                                                                |             | x=0     | x=1     |          |                                  |

|                                                                                | A           | В       | C<br>C  | 0        |                                  |

|                                                                                | B<br>C      | A<br>D  | C       | $0 \\ 0$ |                                  |

|                                                                                | D           | D       | E       | 1        |                                  |

|                                                                                | Е           | A       | F       | 0        |                                  |

|                                                                                | F           | В       | G       | 0        |                                  |

|                                                                                | G           | A       | Е       | 0        |                                  |

| (i) Use an <b>implication table</b> to id <b>implication table and the sta</b> |             |         |         |          |                                  |

| (ii) Show a <b>state graph</b> for the find including inputs and outputs.      | nal irredun | dant m  | achine. | Inclu    | de all information on the graph, |

| 2(a) (10pts)                                                                   |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

|                                                                                |             |         |         |          |                                  |

| 2(b) (10pts) |

|--------------|

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

2(b) Considering the definition of setup time for a latch, is it possible for the setup time for a latch to have a negative value? What would that mean? **Under what conditions can the setup time for a latch be negative?** State all the conditions you can think of and illustrate with an example, where possible.

(3) This problem concerns a base-(-2) (base-(minus-two)) adder. In CS150, we only considered number systems with positive bases (in particular, the binary, or base-2, system). For example, in a base-3 system, the number ABCD<sub>3</sub> is equal to:

$$ABCD_3 = A*3^3 + B*3^2 + C*3^1 + D*3^0.$$

So for a base-(-2) system, EFGH<sub>-2</sub> would be computed using:

$$EFGH_{-2} = E*(-2)^3 + F*(-2)^2 + G*(-2)^1 + H*(-2)^0$$

(a) Convert the following decimal numbers to base-(-2). Use as many bits as you need.

3(a) (8pts)

$$-7_{10} =$$

\_\_\_\_\_\_\_\_

$$5_{10} = \underline{\phantom{0}}_{-2}$$

$6_{10} = \underline{\phantom{0}}_{-2}$   $-7_{10} = \underline{\phantom{0}}_{-2}$   $11_{10} = \underline{\phantom{0}}_{-2}$

- (b) For the purpose of this problem, we define a number system as *contiguous* if, given any two integer values m and n which can be represented in the number system, there exists no integer value x, with m < x < n, that cannot be represented in the system. For example, a 1-bit decimal system is contiguous. It can represent the counting numbers 0-9, and there are no numbers in between 0 and 9 which cannot be represented using one decimal digit. The binary number system (base 2) is also contiguous.

- (i) Is a four-bit base-(-2) system contiguous?

- (ii) What are the maximum and minimum values (in decimal) that can be represented by a four-bit base-(-2) system?

- (iii) Is an n-bit base-(-2) system contiguous, where n is any positive integer? Justify your answer.

3(b) (6pts)

(ii) Maximum<sub>10</sub> = \_\_\_\_\_  $Minimum_{10} =$

(iii)

| (c) Add the following numbers in base-(-2). Pay close | attention to the carry-in and carry-out aspects |

|-------------------------------------------------------|-------------------------------------------------|

| because they are important in Part (d)                |                                                 |

|                                                       |                                                 |

| 3(c) (2pts)                                                 |  |

|-------------------------------------------------------------|--|

| $001110_{-2} + 001111_{-2} = \underline{\hspace{1cm}}_{-2}$ |  |

(d) Draw a truth table for a one-bit bit slice of a base-(-2) adder. Assume one bit of carry-in. You must determine the specification for the carry-out.

|      | determine the specification for the carry-out. |  |  |  |  |

|------|------------------------------------------------|--|--|--|--|

| 3(d) | ) (4pts)                                       |  |  |  |  |

|      |                                                |  |  |  |  |

|      |                                                |  |  |  |  |

|      |                                                |  |  |  |  |

|      |                                                |  |  |  |  |

|      |                                                |  |  |  |  |

|      |                                                |  |  |  |  |

Additional space for Problem 3

| Your Name: |  |

|------------|--|

|            |  |

(4) (a) For the two-input primitive flow table shown on the right, obtain the **merged flow table** by merging states to produce a table with the **minimum possible number of rows**. Show your merger diagram (graph). Assume all outputs are the same value. *Do not* attempt to reduce the table by eliminating equivalent states first; all states *must* appear in your final solution.

| X1 X2 |           |           |                       |  |  |

|-------|-----------|-----------|-----------------------|--|--|

| 00    | 01        | 11        | 10                    |  |  |

| 1 4   | 5 5 5 5 5 | 6 3 3 6 - | 2<br>2<br>-<br>2<br>- |  |  |

| 4. ( | (a) |   | 1 | Λ, | n | <b>(</b> (2) |   |

|------|-----|---|---|----|---|--------------|---|

| 4. ( | a   | • | 1 | VI | U | LS.          | ļ |

Merger diagram and minimum-row merged flow table

Additional space for Problem 4(a)

(4) (b) Obtain a **race-free state assignment** for the merged flow table shown on the right (*not* related to part 4(a)) using **as few additional states as possible**. **List all adjacency constraints. Show all steps and your final state-codes.** (Hint: three state variables are required.)

| X1 X2       |                      |                                                                |                  |

|-------------|----------------------|----------------------------------------------------------------|------------------|

| 00          | 01                   | 11                                                             | 10               |

| ①<br>7<br>7 | (2)<br>(6)<br>6<br>2 | $\begin{bmatrix} 3 \\ \hline 3 \\ \hline 8 \\ 3 \end{bmatrix}$ | 4<br>5<br>4<br>5 |

| 4. (b) (10pts) |  |

|----------------|--|

|                |  |

|                |  |

|                |  |

|                |  |

|                |  |

|                |  |

|                |  |

|                |  |

|                |  |

Additional space for Problem 4(b)